└ 1. 가상 메모리의 개요

1.1. 가상 메모리 시스템

1.2. 매핑 테이블의 필요성과 역할

2. 페이징 기법

2.1. 페이징 기법의 구현

2.2. 페이징 기법의 주소 변환

2.3. 페이지 테이블 관리

2.4. 페이지 테이블 매핑 방식

3. 세그먼테이션 기법

3.1. 세그먼테이션 기법의 구현

3.2. 세그먼테이션 기법의 주소 변환

4. 세그먼테이션-페이징 혼용 기법

4.1. 메모리 접근 권한

4.2. 세그먼테이션-페이징 혼용 기법의 도입

4.3. 세그먼테이션-페이징 혼용 기법의 주소 변환

5. [심화학습] 캐시 매핑 기법

5.1. 캐시 직접 매핑

5.2. 캐시 연관 매핑

5.3. 캐시 집합-연관 매핑

1. 가상 메모리의 개요

1.1. 가상 메모리 시스템

가상 메모리(Virtual Memory)

물리 메모리(실제 메모리)의 크기와 상관없이 메모리를 이용할 수 있도록 지원하는 기술

크기가 다른 물리 메모리에서 일관되게 프로세스를 실행할 수 있는 기술

가상 메모리 시스템의 프로세스는 가상의 0번지부터 시작하는 메모리 공간을 갖는다.

가상 메모리의 최대 크기는 컴퓨터 시스템이 가진 물리 메모리의 최대 크기로 한정한다.

가상 메모리에서 메모리 관리자가 사용할 수 있는 전체 크기는 '물리 메모리 + 스왑 영역'이다.

메모리 관리자는 가상 주소를 실제 물리 주소로 변환하는 작업을 한다.

이를 동적 주소 변환(DAT : Dynamic Address Translation)이라고 한다.

가상 메모리 분할 방식에도 가변 분할 방식과 고정 분할 방식이 존재한다.

가변 분할 방식 기법은 세그먼테이션(Segmentation), 고정 분할 방식 기법은 페이지(Page)라고 한다.

1.2. 매핑 테이블의 필요성과 역할

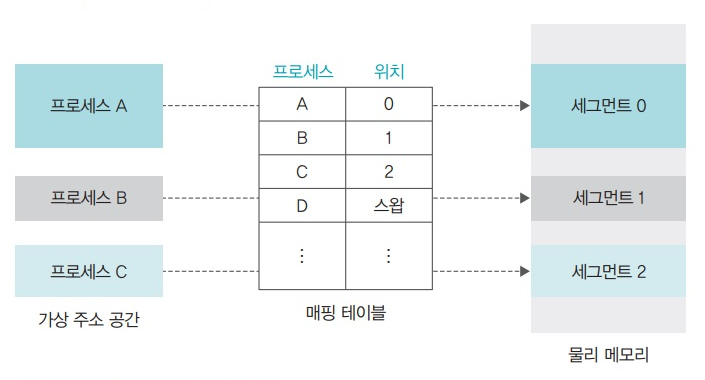

메모리 매핑 테이블은 가상 주소가 물리 메모리의 어느 위치에 있는지 정의하는 테이블이다.

└ 메모리 매핑 테이블, 메모리 테이블, 매핑 테이블이라고도 한다.

└ 페이징 기법을 사용하면 페이지 매핑 테이블(Page Mapping Table) 또는 페이지 테이블이라고 한다.

└ 세그먼테이션 기법을 사용하면 세그먼테이션(Segmentation Mapping Table) 또는 세그먼테이션 테이블이라고 한다.

2. 페이징 기법

2.1. 페이징 기법의 구현

페이징 기법은 고정 분할 방식을 사용하는 가상 메모리 관리 기법이다.

물리 주소 공간을 같은 크기로 나누어 사용하고 항상 0번지부터 시작한다.

가상 주소의 각 분할 영역을 페이지(Page), 물리 주소의 각 분할 영역을 프레임(Frame)이라고 부른다.

이때 페이지와 프레임의 크기는 동일하다.

페이지 테이블은 하나의 열(column)으로 구성한다.

페이지 테이블을 하나의 배열로 봤을 때, 위치를 페이지 값을 프레임이라고 생각하면 된다.

이때 값이 invalid일 경우, 해당 페이지가 스왑 영역에 있다는 뜻이다.

2.2. 페이징 기법의 주소 변환

1. 가상 주소 N번지가 어느 페이지에 있는지 찾는다.

2. 페이지 테이블에 접근해 대응하는 프레임을 찾는다.

3. 프레임에 접근한다.

이때 가상 주소에서 28번지라면 2번 페이지의 8번째 주소라는 의미이다.

36번지라면 3번 페이지의 6번째 주소, 91번지라면 9번 페이지의 1번째 주소. 규칙이 보이지 않는가?

앞 숫자는 페이지, 뒷 숫자는 몇 번째인지 보여준다.

늘 2자리인 것은 아니니 조금 더 정확하게는 페이지 = (N / 10), 주소 = (N % 10)인 것이다.

└ 10으로 나누는 것은 10Byte가 한 페이지의 길이이기 때문이다. 16bit CPU에서는 한 페이지의 길이가 2^10Byte이다.

16bit 컴퓨터가 사용 가능한 가상 메모리 크기는 2^16Byte이다. 고로 0 ~ 65535번지까지 사용 가능하다.

이때 한 페이지의 길이가 2^10Byte이기 때문에, 16bit 중 10bit는 D, 6bit는 F로 사용한다.

정리하자면 한 페이지의 길이가 2^10(1024)Byte인 것이 2^6(64)개 있다는 의미이다.

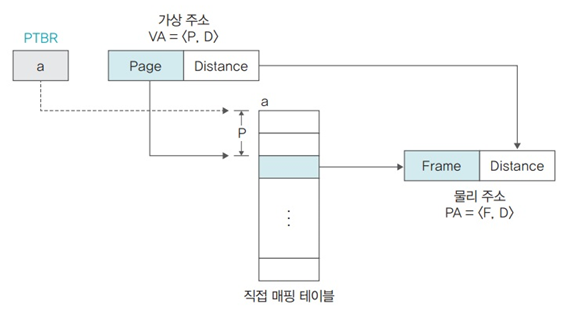

VA = <P, D> → PA<F, D>

이 공식을 정의한 것이 VA = <P, D>이다.

└ VA(Virtual Address) : 가상 주소의 번지

└ P(Page) : 페이지의 위치

└ D(Distance or Offset) : 페이지의 처음 위치에서 해당 주소까지의 거리

가상 주소를 VA로 정의한 것처럼 물리 주소는 PA = <F, D>이다.

└ PA(Physical Address) : 물리 주소의 번지

└ F(Frame) : 프레임의 위치

└ D(Distance) : 프레임의 처음 위치에서 해당 주소까지의 거리

페이지 테이블은 페이지 번호와 프레임 번호로 구성하며, 각각의 줄은 PTE(Page Table Entry)로 구분한다.

PTE는 프레임 번호만 가지지만 이것은 정렬되어있다는 것이 전제 조건이다.

정렬되지 않은 페이지 테이블이라면, PTE는 페이지 번호와 프레임 번호의 2가지 요소를 갖는다.

2.3. 페이지 테이블 관리

문제는 프로세스마다 페이지 테이블이 하나씩 존재한다는 점이다.

메모리 관리자는 특정 프로세스를 실행할 때마다 해당 페이지 테이블을 참고해 가상 주소에서 물리 주소로 변환한다.

페이지 테이블이 필요 시 빠른 접근을 위해, 물리 메모리 영역 중 OS 영역의 일부분에 모아놓는다.

각 페이지 테이블의 시작 주소를 PTBR에 보관하여 속도를 더욱 높인다.

└ PTBR(Page Table Base Register) : 페이지 테이블 기준 레지스터

프로세스가 많아지면 OS가 실제 사용할 수 있는 영역이 줄어든다. 그래서 스왑 영역을 같이 사용한다.

2.4. 페이지 테이블 매핑 방식

직접 매핑(Direct Mapping) : 페이지 테이블 전체가 물리 메모리의 운영체제 영역에 존재하는 방식

연관 매핑(Associative Mapping) : 페이지 테이블 전체를 스왑 영역에서 관리하는 방식

집합-연관 매핑(Set-Associative Mapping) : 연관 매핑의 문제를 개선한 방식

역매핑(Invert Mapping) : 반대로 프레임을 기준으로 페이지 테이블을 구성하는 방식

직접 매핑(Direct Mapping)

위에서 언급한 가장 단순한 방식이다. PTBR을 통해 VA = <P, D> → PA<F, D>의 방식이다.

연관 매핑(Associative Mapping)

전체 페이지 테이블을 스왑 영역에서 관리하고 일부분만 물리 메모리에 가져와 사용하는 방식이다.

이 일부분의 테이블을 TLB 또는 Associate Register라고 부른다.

└ TLB(Translation Look-Aside Buffer) : 변환 색인 버퍼

원하는 데이터가 찾을 때 가장 먼저 TLB를 확인한다.

이때 원하는 페이지 번호가 TLB에 있는 경우, TLB Hit라고 한다.

원하는 페이지 번호가 TLB에 없는 경우, TLB Miss라고 하며 스왑 영역에서 직접 매핑을 사용해 프레임 번호로 변환한다.

└ 작동 방법이 Cache(Cache Hit, Cache Miss)와 유사하다.

당연하게도 물리 메모리를 절약할 수 있지만, TLB Miss가 잦을수록 시스템의 성능은 떨어진다.

집합-연관 매핑(Set-Associative Mapping)

직접 매핑과 유사한 방식으로 VA = <P1, P2, D> → PA<F, D> 구조를 따른다.

페이지 테이블을 같은 크기의 여러 묶음으로 나눈다. 각 묶음의 시작 주소를 가진 디렉터리 테이블을 새로 만든다.

디렉터리(Diretory)는 파일들을 묶어놓는 하나의 집합이다. 이런 방식을 사용해 Directory Mapping이라고도 한다.

VA = <P1. P2, D>에서 P1은 디렉터리 테이블 위치를, P2는 묶음 내에서의 위치를 가리킨다.

앞서 가상 주소 32를 3, 2로 나누었다면 여기서는 0, 3, 2로 나누는 것이다.

172는 17, 2가 아니라 1, 7, 2로 2835는 283, 5가 아니라 28, 3, 5로 나누어 페이지 주소를 세분화한다.

P1은 P2가 메모리 영역인지 스왑 영역인지에 대한 정보도 같이 나타낸다. 때문에 Multi-Page Mapping이라고도 한다.

역매핑(Invert Mapping)

직접 매핑, 연관 매핑, 집합-연관 매핑은 모두 가상 주소를 기준으로 프레임을 매핑한 방식이다.

역매핑은 반대로 프레임 번호를 기준으로 테이블을 작성한다.

3. 세그먼테이션 기법

3.1. 세그먼테이션 기법의 구현

세그멘테이션 기법도 페이징 기법처럼 테이블을 사용하여 가상 주소와 물리 주소를 매핑한다.

이 테이블을 Segmentation Table 또는 Segmentation Mapping Table이라고 한다.

구성 요소는 세그먼트의 크기를 나타내는 Limit와 물리 메모리 시작 주소를 나타내는 Address이다.

└ 자신에게 주어진 영역을 넘어가면 안 된다는 의미에서 size 대신 limit라는 단어를 사용한다.

3.2. 세그먼테이션 기법의 주소 변환

1. 가상 주소 N번지가 어느 세그먼테이션에 있는지 찾는다.

2. 세그먼테이션 테이블에 접근해 대응하는 물리 시작 주소를 찾는다.

3. Distance가 세그먼트의 크기보다 크다면 오류를 출력하고, 크지 않다면 물리 주소를 구한다.

4. 물리 주소에 접근한다.

이때 세그먼테이션을 활용한 가상 주소를 VA = <S, D>라고 표현한다.

└ VA(Virtual Address) : 가상 주소의 번지

└ S(Segmentation) : 세그먼트 번호

└ D(Distance) : 세그먼트 시작 지점에서 해당 주소까지의 거리

만약 접근하려는 세그먼테이션을 초과한 주소에 접근하려면 오류를 발생하고 프로세스를 강제 종료한다.

이 오류를 Trap이라고 한다. 메모리 주소를 벗어나는 곳에는 접근할 수 없기에 D는 메모리 보호의 의미도 지닌다.

반대로 사용자가 의도하여 중지시키는 인터럽트는 Signal이라고 한다.

4. 세그먼테이션-페이징 혼용 기법

4.1. 메모리 접근 권한

메모리 접근 권한은 메모리의 특정 번지에 데이터를 사용할 수 있는 권한이다.

읽기(Read), 쓰기(Write), 실행(Execute), 추가(Append)가 있지만, 쓰기 권한이 있어야 추가할 수 있어서 같이 취급한다.

왼쪽의 '메모리 접근 권한' 그림과 같이 8가지 접근 방식이 있다.

어떤 파일을 읽기 없이 쓰기만 하는 경우는 거의 없어 모드 2와 3은 사용하는 일이 거의 없다.

메모리 접근 권한 검사는 가상 주소에서 물리 주소로 주소 변환이 일어날 때마다 실행해 유효한 접근인지 확인한다.

자기 자신을 수정하는 프로그램은 없기에 코드 영역은 읽기 및 실행 권한만을 가진다.

읽기만 가능한 데이터도 있고, 읽기 쓰기가 모두 가능한 데이터가 있다. 따라서 데이터 영역은 그림과 같은 권한을 갖는다.

4.2. 세그먼테이션-페이징 혼용 기법의 도입

각 페이지마다 접근 권한이 다르기 때문에 페이지 테이블에 권한 비트(Right Bit)를 추가하여 테이블을 작성한다.

메모리 관리자는 주소 변환이 이루어질 때마다 페이지 테이블의 권한 비트를 확인해 유효한 접근인지 판별한다.

각 페이지마다 권한 비트를 기입해야 한다면 페이지 테이블의 크기는 커지게 된다.

따라서 같은 권한이 있는 페이지끼리 모아, 세그먼테이션 테이블로 관리한다.

└ 권한 비트를 세그먼테이션에 적고, 권한 비트를 갖는 페이지 테이블의 시작 주소를 적으면 테이블 크기를 줄일 수 있다.

현재 대부분의 운영체제 이 방식을 사용한다.

4.3. 세그먼테이션-페이징 혼용 기법의 주소 변환

VA = <S, P, D>에서 S는 Segmentation Number, P는 Page Number, D는 Distance이다.

여태껏 설명한 페이징 기법, 세그먼테이션 기법을 섞었을 뿐이지 방식은 같으므로 자세한 설명은 생략한다.

5. [심화학습] 캐시 매핑 기법

위에서 설명한 매핑 방식은 가상 주소를 물리 주소로 변환하는 매핑 방식이다.

지금 목차는 캐시(Cache) 메모리가 사용할 데이터를 예측해서 가져올 때 사용하는 매핑 방식이다.

같은 매핑이라는 단어를 사용하고 있지만, 목적과 방법이 다르다는 것을 기억해야 한다.

사진과 함께 짧은 설명만 적어서 공부할 예정이다.

5.1. 캐시 직접 매핑

메모리의 페이지 수를 캐시 페이지 수로 나눈 것을 Block이라고 한다.

그리고 각 Block마다 변호를 명시하는데 이것을 Tag라고 부른다.

위의 사진을 예로 들면, 메모리는 16B, 캐시는 4B라 메모리를 4개의 블록으로 나누었다.

Tag와 bd(Block Distance; 블록에서의 거리, 위치)를 보고 메모리에서 캐시로 데이터를 옮긴다.

Tag와 bd가 정해진 위치의 캐시 메모리에만 올라오기 때문에 Cache Hit나 Cache Miss가 빠르다.

하지만, CPU가 한 Tag나 한 bd만을 요구하면 금방 캐시 메모리에서 쫓겨나는 문제가 있다.

5.2. 캐시 연관 매핑

캐시 직접 매핑에서의 문제점은 요구하는 메모리 주소가 비슷할 경우에, 캐시에서 데이터가 금방 쫓겨난다는 거다.

이를 방지하기 위해 Tag와 bd를 하나의 값으로 보아 메모리를 자유롭게 사용하게 만들었다.

캐시에서 운이 좋으면 금방 Cache Hit가 되지만 Cache Miss가 나면 메모리의 모든 주소를 검색하는 단점이 있다.

5.3. 캐시 집합-연관 매핑

캐시에 집합을 여러 개(K개) 둔 방식이다. 그리고 각 집합마다 직접 매핑을 실행한다.

이러면 bd가 같은 데이터가 K개가 생기지만 캐시 메모리도 K개라서 모든 데이터를 찾지 않고 Cache Hit가 가능하다.

위의 그림에서는 캐시 집합이 2개(K = 2)이고, 각 집합마다 2개의 페이지를 사용하게 했다.

2개의 페이지를 사용하고 메모리는 16B이니 Tag는 총 8개이다.

주소 P는 4bit인데 8개의 위치를 알려주어야 하니 3bit를 사용하고 bd는 남은 1bit를 사용한다.

집합 1에서 <000, 0> 데이터와 <110, 1> 데이터를 사용하고 있다고 해보자.

이때 <110, 0>을 캐시에 가져오고 싶으면 집합 2를 사용하면 된다.

'학교 공부 > 스마트 운영체제' 카테고리의 다른 글

| 운영체제 10 입출력 시스템과 저장장치 (0) | 2022.05.24 |

|---|---|

| 운영체제 09 가상 메모리 관리 (0) | 2022.05.17 |

| 운영체제 07 물리 메모리 관리 (0) | 2022.05.03 |

| 운영체제 06 교착 상태 (0) | 2022.04.19 |

| 운영체제 05 프로세스 동기화 (0) | 2022.04.12 |